北京打樣PCB價格信息

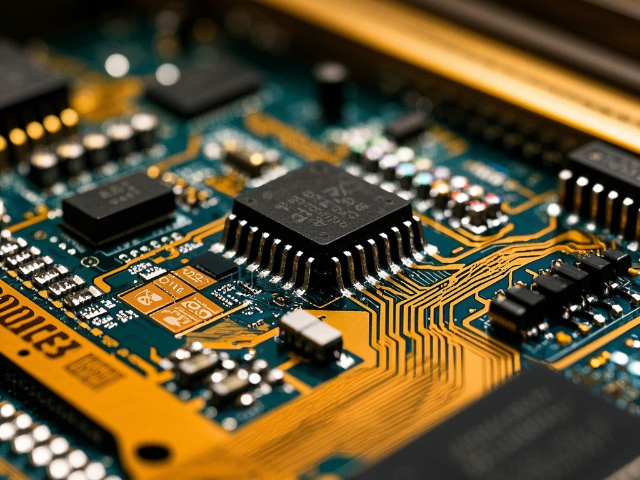

Chiplet基板設計與制造技術

Chiplet基板采用高密度互連(HDI)技術,線寬/間距突破2μm,支持2.5D/3D封裝。采用RDL再布線技術,層間互聯通過微凸塊(Microbump)實現,間距<50μm。材料選擇方面,陶瓷基板(如AlN)熱導率>170W/(m?K),適合高功率場景;有機基板(如BT樹脂)成本低,適合消費電子。工藝要點:①激光直接成像(LDI)實現線寬±5μm;②化學機械拋光(CMP)控制表面平整度;③微凸塊共面性≤5μm。測試驗證:某Chiplet基板通過1000次熱循環測試(-40℃~125℃),阻抗變化<3%,滿足長期可靠性要求。市場前景:據Yole預測,2025年Chiplet基板市場規模將達60億美元,年復合增長率28%。 31. Mentor Graphics Xpedition 支持自動扇出設計,減少人工干預。北京打樣PCB價格信息

航空航天PCB可靠性設計

航空航天PCB通過MIL-PRF-31032認證,耐溫-55℃~260℃。采用鋁基復合材料,熱膨脹系數與芯片匹配,減少熱應力失效。表面處理采用化學鍍鎳金,厚度≥0.05μm,抗腐蝕性能達500小時鹽霧測試。工藝要求:①通孔銅厚≥35μm;②鍍層孔隙率<1個/cm2;③標識采用激光打標,耐溫>300℃。應用案例:某衛星電路板使用該設計,在太空環境中穩定運行10年以上。測試標準:通過NASA標準測試,包括輻射、真空、微隕石沖擊等。 中山PCB阻抗計算方法0603 封裝電容焊盤間距建議 0.5mm,避免回流焊時出現墓碑效應。

沉金工藝(ENIG)質量控制

沉金工藝(ENIG)鎳層厚度控制在3-5μm是關鍵,過薄易導致金層滲透失效,過厚則增加脆性風險。建議使用XRF檢測儀在線監控鎳層厚度,偏差控制在±0.5μm以內。金層厚度需≥0.05μm,表面粗糙度Ra≤0.4μm,接觸阻抗<50mΩ。缺陷分析:黑盤缺陷(鎳層氧化)主要由活化液濃度不足或水洗不徹底引起。解決方案:定期檢測活化液Pd2+濃度(建議5-8ppm),增加DI水清洗次數至3次,確保殘留Cl?<5ppm。材料選擇:推薦使用含P量5-7%的化學鎳配方,可平衡耐腐蝕性與焊接性。對于存儲周期>6個月的產品,建議采用沉金+OSP復合工藝。壽命測試:通過HAST加速老化測試(130℃,85%RH,200小時),金層腐蝕速率需<0.01μm/天,接觸電阻變化<10%。

未來PCB技術挑戰與機遇

未來PCB面臨的挑戰包括:更高集成度(如Chiplet)、更低功耗(如量子計算)、更嚴格環保要求(如可降解材料)。機遇在于新能源汽車、AI服務器、6G通信等新興領域的需求增長。企業需加大研發投入,布局先進封裝、智能生產等技術。戰略建議:①建立聯合實驗室開發前沿技術;②引入AI優化設計與生產;③構建綠色供應鏈體系。市場洞察:據Yole數據,2025年先進封裝基板市場規模將達200億美元,年復合增長率15 .%。 18. DFM 分析需包含 SMT 貼裝性評估,推薦使用 DFMEA 工具。

微帶線阻抗計算與優化

微帶線阻抗計算需綜合考慮板材介電常數(εr)、線寬(W)、介質厚度(H)等參數。以FR4板材(εr=4.4)為例,線寬0.3mm、介質厚度0.15mm時,50Ω阻抗對應線長匹配誤差需<5mil。高頻場景推薦使用RogersRO4350B材料(εr=3.48±0.05),插入損耗<0.15dB/in@10GHz。仿真驗證:通過SIwave仿真工具建立三維模型,優化走線避免直角拐點(改用45°或圓弧過渡),減少信號反射。實測數據顯示,優化后回波損耗從-15dB提升至-20dB。行業趨勢:對于100Gbps高速背板,差分阻抗需嚴格控制在100Ω±5%,采用半固化片預浸料(如Isola370HR)可穩定阻抗性能。線長匹配誤差需<3mil,通過蛇形走線補償。制造工藝:蝕刻線寬公差控制在±5μm,采用LDI激光直接成像技術可提升精度。某企業通過工藝優化,阻抗合格率從85%提升至98%。 44. 焊盤不上錫可能由 OSP 膜過厚或焊接溫度不足導致。中山怎樣選擇PCB設計服務

35. 立創 EDA 支持 Gerber 文件在線驗證,實時反饋生產問題。北京打樣PCB價格信息

激光直接成像(LDI)技術

激光直接成像(LDI)技術分辨率達5μm,適用于0.1mm以下線寬。相比傳統菲林曝光,對位精度提升3倍,減少返工率25%。支持復雜圖形(如盲孔、微槽)一次成型。設備參數:①激光波長355nm;②掃描速度100-200mm/s;③能量密度100-200mJ/cm2。應用案例:某HDI板廠采用LDI技術,線寬公差從±10μm提升至±5μm,良率從92%提升至96%。成本分析:LDI設備投資約800萬元,年維護成本約50萬元,適合中高級板生產。。 北京打樣PCB價格信息

- 蕪湖設備大功率電源市場價格 2025-04-28

- 昆明光電示波器 2025-04-28

- 東莞設備示波器維修電話 2025-04-28

- 深圳專注大功率電源廠家報價 2025-04-28

- 黃浦區實時性強示波器供應商家 2025-04-28

- 長沙萬用表用戶體驗 2025-04-28

- 品牌示波器用戶體驗 2025-04-27

- 深圳校驗示波器結構 2025-04-27

- 杭州設備大功率電源解決方案 2025-04-27

- 東莞波形直觀示波器價格信息 2025-04-27

- 北京可程式淋雨試驗房采購 2025-04-28

- 江西不銹鋼防爆污水流量計安裝規范 2025-04-28

- 西藏進口拉繩位移傳感器品牌 2025-04-28

- 新加坡MIRI TL 12時差培養箱內置Time-lapse拍照系統 2025-04-28

- 新吳區特殊柴油流量計調試 2025-04-28

- 智能化顯微CT推薦咨詢 2025-04-28

- 山西SRM型管狀電加熱器 2025-04-28

- 吉林對比流量氣密檢漏儀泄漏設備廠家 2025-04-28

- 寧夏自凈式無管通風柜價格 2025-04-28

- 廣東旋轉氣缸電話 2025-04-28